ファブリツィオ・フランチオーネ

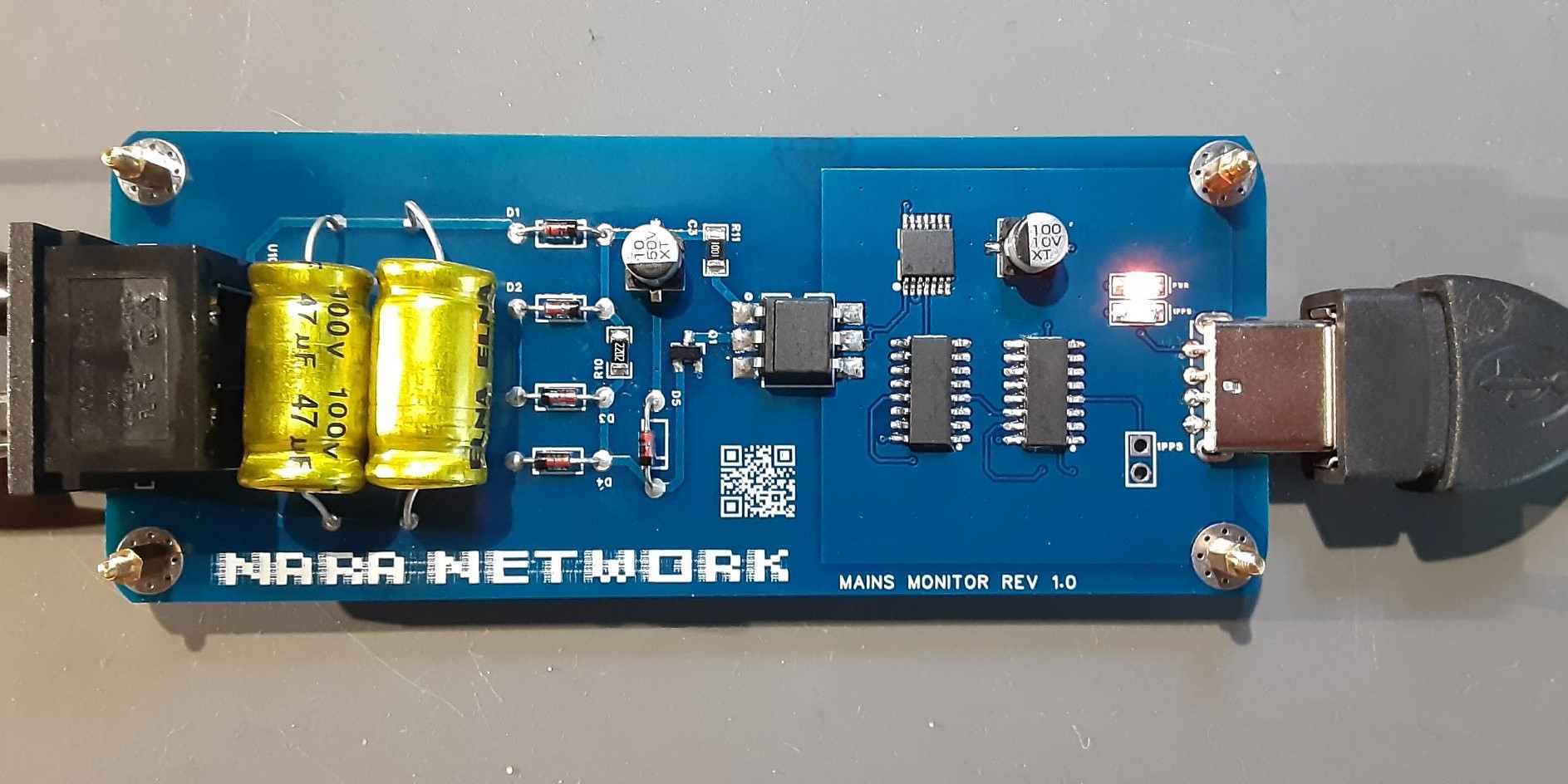

周波数と位相を捕捉する回路は比較的単純です:ダウンステップトランスが電圧を9VACに下げ、ゼロクロス回路に到達します。

その後、シュミット・トリガーがDCエリアの信号を2つの分周器に渡し、主電源の周波数を1Hzに下げます。

周波数は1Hzに検出され、ラップトップのシリアルラインに供給される。

主電源周波数を取得するためのソフトウェアは、U.Windlによっ て書かれたRFC2783の修正版である。

コンピュータ・システムにPPS信号を供給する便利な方法の1つは、その信号をシリアル・ラインの モデム・コントロール・ピンに接続することである。

をコンピュータに接続するためのインタフェースです。 データキャリア検出(DCD)ピンは、この目的で頻繁に使用されます。 のタイムコード出力は,一般的に

を同じシリアル回線でコンピュータに送信します。 コンピュータは、DCDピンの信号遷移を検出します、

通常、割り込みを受けることによって、できるだけ早くタイムスタンプを記録する。

この機能の典型的な用途は、オペレーティングシステムができるだけ早く高解像度のタイムスタンプを 記録(「キャプチャ」)することです。

は、PPS信号の遷移(通常は割り込みによって示される)を検出した後、このタイムスタンプを利用 することができます。 このタイムスタンプを利用することで、より少ないコストで、より多くの情報を得ることができます。

を、時間関連ソフトウェアに送信する。 ソフトウェアは、キャプチャしたタイムスタンプと受信したタイムコードを比較することで

は、システムクロックと正確な時間ソースとの間のオフセットを正確に発見することができます。

このAPIの主な目的は、真のパルス毎秒イベントを捕捉することですが、APIはまた、正確なパル ス毎秒イベントを捕捉するために使用されることもあります。

また、他の期間のイベントや、非周期的なイベントであっても、信号の遷移として表現できる場合に は、タイムスタンプを付与することができる。

原理的には、捕捉するイベントのレート、すなわち信号の頻度は、1日1回(またはそれ以下の頻度) から、数

千/秒となる。 しかし、ほとんどの実装では、タイムスタンプ機能は、プロセッサの割り込みとして、次のように実装されます。

が比較的高い優先度を持つ場合、そのようなイベントの発生率を制限することが賢明である。 これは、以下のようなハードウェアのメカニズムによって行うことができます。

が信号を発生させるか、OSによって発生させる。

C言語によるコードの基本的な実装は、パルス毎秒の信号の「アサート」と「クリア」の信号を受信す るように設定されていますが、

50Hzが比較的低速であることに関連する限り、他のタイプも記録することが可能です。

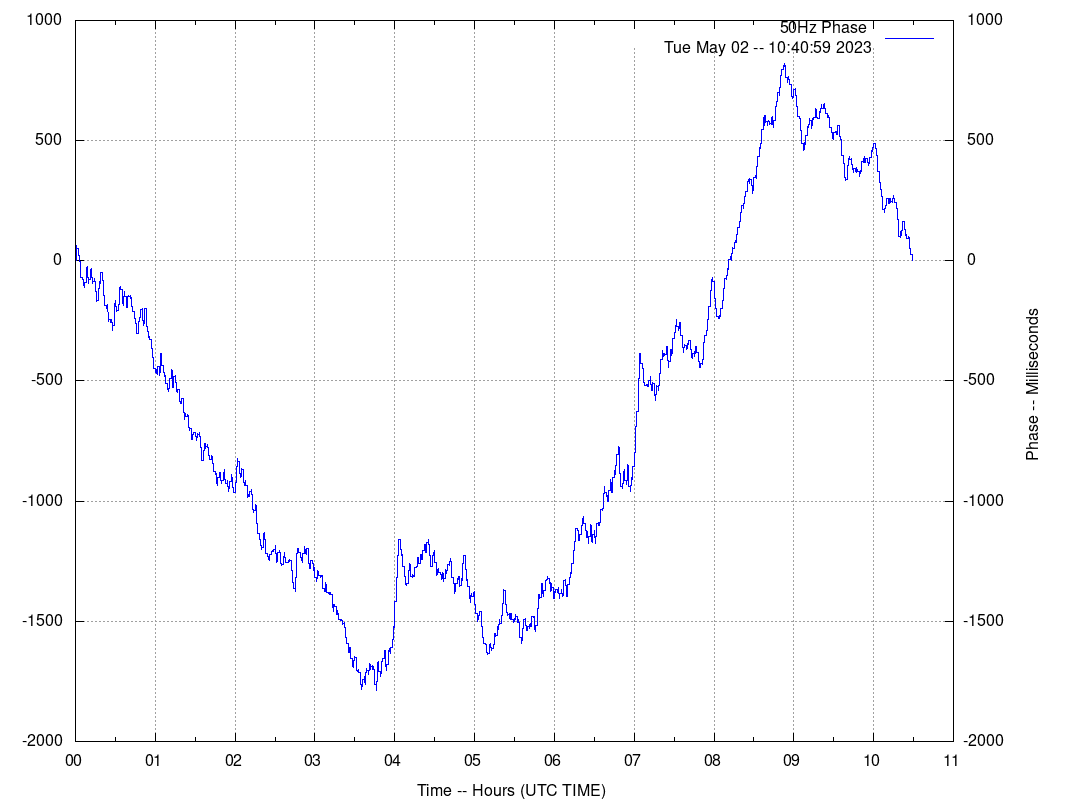

周波数のすべてのサイクルをキャプチャし、後で他のプログラムで処理することで、例えば位相を詳細 に抽出し、セットアップ#。

をタイムスタンプ付きでフォーマットし、後でGNUPLOTでグラフに描画します。

9V(DBレベル)のAC電源(50Hz)を接続した場合の例です:

RFC

2783は、スクリプトがデータを操作するために、シリアルラインからの出力をより良く、より明確にするために、少し変更されています。

RFC

2783は、スクリプトがデータを操作するために、シリアルラインからの出力をより良く、より明確にするために、少し変更されています。以下は、生出力の例です:

assert 3430832 time 1683003744.594031762 delta 0.019984925 offset -405968238 jitter -11174

assert 3430833 time 1683003744.614030934 delta 0.019999172 offset -385969066 jitter 14247

assert 3430834 time 1683003744.634016207 delta 0.019985273 offset -365983793 jitter -13899

assert 3430835 time 1683003744.654010141 delta 0.019993934 offset -345989859 jitter 8661

assert 3430832はア サート番号です。(本APIで はPPS)信号は、一連のパル スで構成され、各パルスは "アサート"

(論理真)フェーズと、"クリ ア"(論理偽)フェーズがあり ます。 2つのフェーズは異なる長さであってもよい。 APIは、"assert "フェーズをキャプチャすることができる。

に遷移した瞬間の「タイムスタ ンプ」と、アサート相に遷移し た瞬間の「クリアタイムスタン プ」です。

クリアフェーズ DCDベースのPPSをサポー トする実装者への注意事 項: TTLとRS-232C(V.24/V.28)インターフェースは、どちらも「真」の状態を「真」と定義しています。

のうち、最も高い正電圧を持つ ものを指す。TTLでは公称電 圧のない状態を「偽」の状態と 定義しているが、RS- 232C(V.24/V.28) では

は、負の電圧の存在によって 「偽」の状態を定義する。

PPSパ ルスではなく周波数を測定する ためには、アサート電圧のピー クを連続的に捕捉すれば十分で あり、その効果は証明されてい る、

サウンドカードから検出された 周波数を広帯域スペクトラムア ナライザーで比較すると(ペー ジの最初の2画面)、次のこと がわかります。

は、スペクトル上のすべての周 波数サイクルの変化に従うこと を保証します。しかし、これに ついては、位相測定と同様にさ らなるテストが提供される予定 です

time 1683003744.594031762 は、 ナノ秒の精度で検出されたタイ ムスタンプで、UNIX時間で 表現されます。

NTPプロトコルでは、「タイ ムスタンプは64ビットの符号 なし固定小数点数で表され、 1900年1月1日の0hを基 準とした秒数で表されます。と なっています。

整数部分は最初の32ビット、 分数部分は最後の32ビットに ある[...]この表現の精度 は約200ピコ秒である」。

しかし、ほとんどのコンピュー タシステムでは、この分解能で 時間を測定することはできませ ん(これは5GHzのクロック レートを表しています)。 POSIXのgettimeofday()は

関数は、1マイクロ秒の分解能 を持つ "struct timeval "値を返します。 POSIXのclock_gettime()関数は、1マイクロ秒の分解能を持つ "struct timeval "を返す。

timespec "値で、1ナノ秒の分解能を持つ。

delta 0.019984925 は、2つのタイムスタンプの時間差である。

offset -405968238 マシンの現在の秒数あたりのオフセットです。

jitter -11174イベントタイムスタンプ間のジッター(デルタのデルタ)

時間同期

ノートPCの時計をGPSや原子時計などの信頼できる時刻源と同期させ、測定できるようにするためです。

NTPDよりも高速で、より優れたアルゴリズムを使用しているため、電力線サイクルごとに、従来のNTPの代わりに Chronyが使用されています。

は、ローカルクロックを可能な限りソースに忠実に維持します。

Chronyは、断続的なネットワーク接続、混雑したネットワークなど、さまざまな条件下で優れた性能を発揮します、

温度変化の激しいシステム(通常のコンピュータの時計は温度に敏感)、連続動作しないシステム、仮想マシン上で動作する システム。

インターネット上で同期した2台のマシン間の精度は、通常、数ミリ秒以内、LAN上のマシンでは数十マイクロ秒以内で す。

ハードウェアタイムスタンプやハードウェアリファレンスクロックを使用すれば、2台のマシンの同期精度をサブマイクロ秒 レベルまで向上させることができるかもしれません。

Chronydの典型的な出力は以下の通りです:

Reference ID : 179C519B (v172-105-221-80.ntp.tyo2l.rnode.jp)

Stratum : 4

Ref time (UTC) : Tue May 02 08:51:02 2023

System time : 0.000000048 seconds fast of NTP time

Last offset : -0.002801925 seconds

RMS offset : 0.010625760 seconds

Frequency : 24.133 ppm slow

Residual freq : -0.591 ppm

Skew : 10.939 ppm

Root delay : 0.026025012 seconds

Root dispersion : 0.004074866 seconds

Update interval : 64.2 seconds

Leap status : Normal

これは、50/60Hzのような低速の周波数を測定するには十分すぎるほどです。

NTPDとchronydの違い -- chronydがntpdより優れている点:

chronydは、時刻参照へのアクセスが断続的な環境でもうまく機能しますが、ntpdは時刻参照の定期的なポーリン グがないとうまく機能しません。

chronydは、ネットワークが長時間混雑していても、うまく動作することができます。

chronydは通常、より速く、より正確に時計を同期させることができます。

chronydは、例えば水晶発振器の温度変化によるクロックのレートの急激な変化にも素早く対応することができます、

一方、ntpdは再び落ち着くまで長い時間を必要とすることがあります。

デフォルトの設定では、chronydはシステム起動時にクロックが同期された後、他の実行中のプログラムを動揺させな いようにするために、時間をステップさせない。

ntpdも時刻を変更しないように設定できますが、クロックを調整する別の手段を使用する必要があります。

時計の精度に悪影響を及ぼすなどの欠点がある。

chronydは、Linuxシステム上の時計のレートをより大きな範囲で調整することができるため、以下のようなマシ ンでも動作させることができます。

時計が壊れたり、不安定になったりする。例えば、いくつかの仮想マシンでは。

chronydは小さく、メモリ使用量も少なく、必要なときだけCPUを起動させるので、省電力に有利です。

タイムスタンプから周波数と位相を開発するのは複雑ではありません。ここでは、Pythonによる一連のスクリプトを使 用して、変換と

をBASHで作成し、システムインテグレーションとウェブサーバーへのアップロードを行いました。

Numpy、Pandas、Allantoolsを使用して、周波数を抽出するプログラム(オリジナルバージョンは 2016年に私自身が作成したもので、ソースを確認してください)を作成しました。

timestampsシリーズ :

1683024301.930496255

1683024301.950496125

1683024301.970494527

1683024301.990498168

1683024302.010481345

を最終的な結果に結びつけます:

49.95048

49.99995

49.99578

50.00889

49.95823

50.04406

49.95823

50.00293

このプログラムでは、位相についても同様のことが可能です:

9.363841078166225407e-02

9.435858739256458572e-02

5.752876400347094882e-02

5.467894061437698905e-02

5.360911722527959139e-02

5.253929383618219373e-02

1.034947044708541680e-02

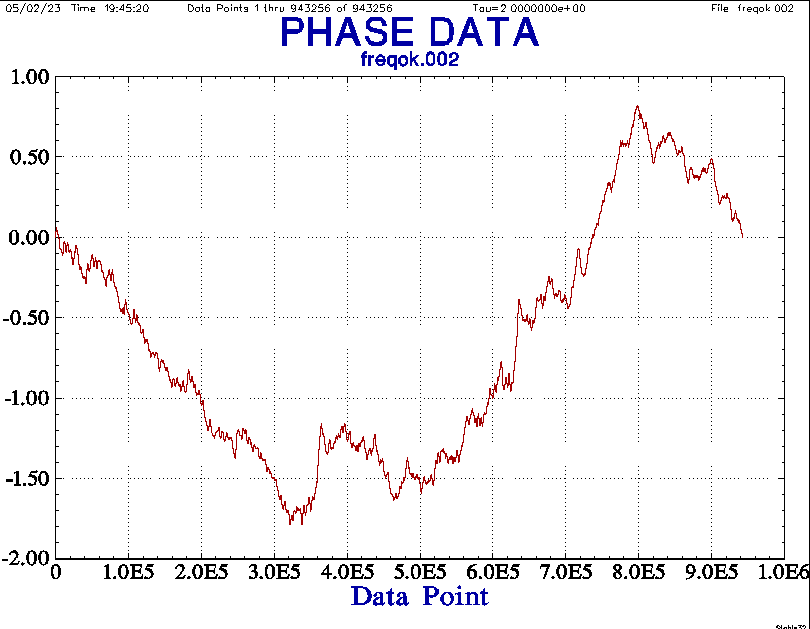

精度を比較するために、同じ周波数出力を時間/周波数測定用の最も有名なソフトウェアの1 つであるStable32で試してみました。

そこでは、位相が抽出され、書かれたpythonプログラムからの同じものと比較されました。念のため、データ結果が同 じ(そして正しい)であることを確認しています:

データの正規化およびキャプ

チャ技術

データの正規化およびキャプ

チャ技術過 去に他の人がやったように(そして彼らは地元の電源に不満を持っていた!)、DCDシリアルピンを使って主電源 からの周波数を測定していました、

少なくともゼロクロスやシュミットトリガーを使わずにどうやって周波数を測定するのだろうと思っていました。 50Hz/60Hzを適切なフィルターなしで捕捉した結果、振幅変調された信号から

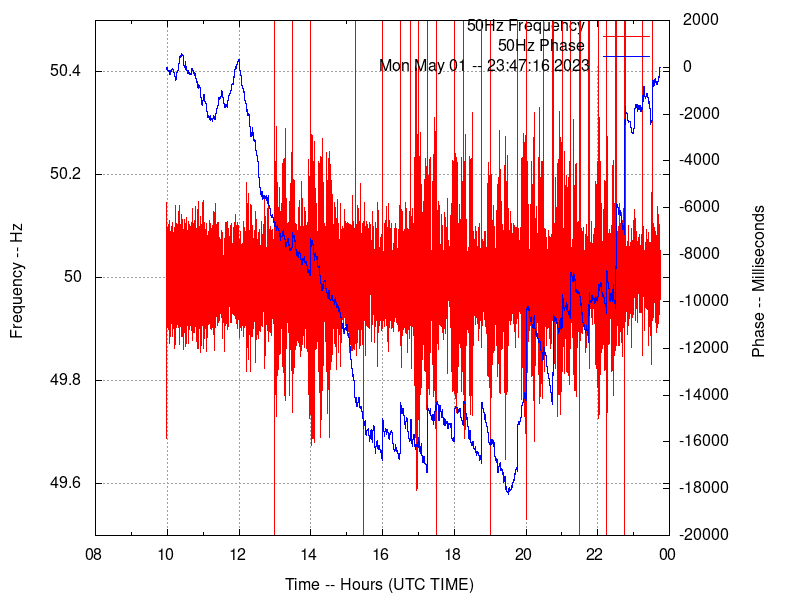

振幅変調された信号とノイズから適切なフィルターをかけずに50Hz/60Hzを捕捉した結果、タイムシフトという点で測定 位相に壊滅的な影響を及ぼしました。これは、次のような例です。

9VACトランスをシリアルラインに直接接続し、そのままキャプチャした例です:

位相が完全にずれていることは明らかで、主電源のノイズによる

18秒(!)の遅延も同様に捉えられています!

位相が完全にずれていることは明らかで、主電源のノイズによる

18秒(!)の遅延も同様に捉えられています!時々、小さな不具合が発生する可能性があるが、主電源が地域の電化製品によって非常に妨害されている場合はなお さらである。

それらを避けるために、パイソンで書かれた前方-後方指数加重移動平均(FBEWMA)アルゴリズムが使用され ている。

この方法により、データの正規化がより自然になり、いくつかの不具合による小さなギャップを埋めることができ、 この手法により劇的に改善された。

FBEWMA実装前の主電源ノイズによるグリッチ(不具合)のあるデータ:

時々、小さな不具合が発生する可能性があるが、主電源が地域の電化製品によって非常に妨害されている場合はなお さらである。

それらを避けるために、パイソンで書かれた前方-後方指数加重移動平均(FBEWMA)アルゴリズムが使用され ている。

この方法により、データの正規化がより自然になり、いくつかの不具合による小さなギャップを埋めることができ、 この手法により劇的に改善された。

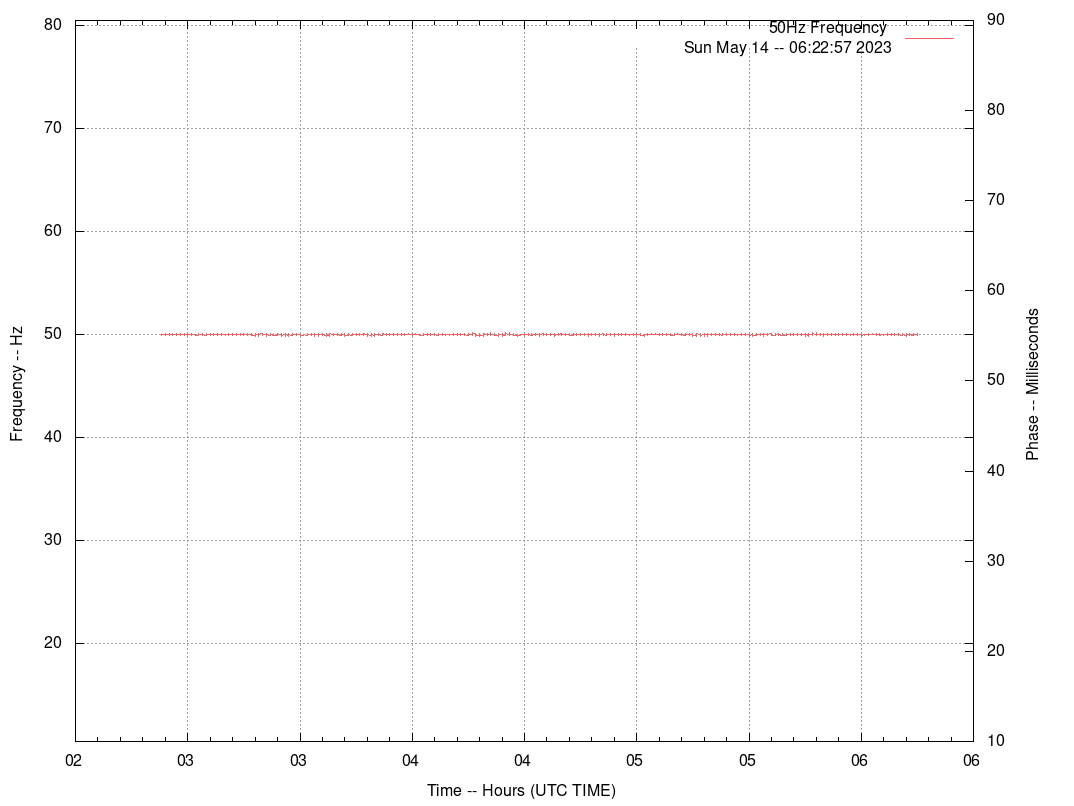

FBEWMAの後 に:

--更新-- 01/27/2025

周波数/位相データのグラフを予備的に分析すると、次のことがわかる。

パワーグリッド・データをモニターし、またシステム応答から

また、システム応答からも:

このGIFは約3ヶ月分のデータを示している(3.36 MB)

周波数は周期の逆数である。しかし、送電網の主電圧の経過を見ると、基本周波数に加えて、高調波、副高調波、位相ジャンプ、電圧変動

など、多数の接続されたフィーダーや消費者によって発生する多くの成分が見える。したがって、主電源周波数は物理的な意味での周波数

ではなく、様々な回転ベクトルの和である。誤った測定結果を避けるために、特に送電網における動的なプロセスの場合には、このことを

考慮に入れなければなりません。

ロードフロー計算は、発電事業者がスケジュールを提出する際に事前に実施され、また、危機的な状況を特定し、必要であれば再割り当て

によってロードフローを変更するために、ネットワークの運用中にも実施される。

NNJシステムに関して、まず第一に、FBEWMAは、どんな小さなグリッチにも関係しないスパイク(それらの99%は、最初の

フィルターとシュミット・トリガーによってすでに除去されている)を保存して、期待通りに本当にうまく機能している。これらのスパイ

クは、例えばアニメーションGIFの14:00のように、ほぼ毎日一貫して定期的に見られますが、おそらく、ネットワーク上のカジュ

アルな負荷に対して周波数を一定に維持するために、毎日のルーチンの間に時間スケジューリングされた発電機が起動したり停止したりす

ることに関連しています。

また、発生する可能性のある時間偏差に対して、送電網を可能な限り一直線に保つために、予定された(そしておそらく自動化された)周

波数の上昇/下降(その後、位相も)を評価することも可能である。